Поскольку “влезаемость” кода в плисину нормальная, нарисовал для Скальпеля вычислительную плату.

Проверю ее немного, и буду заказывать.

Персональная страничка Ампернута

Блог о электрометрии, о моих разработках, о жизни.

Записи моего старого бложика “Радиокружок”

Задолбал я вас со своим хайтехом?  На-те… расслабьтесь…

На-те… расслабьтесь…

Joosphp в очередной раз ездил в ЧЗО, в результате набрал несколько проб и прислал их мне на анализ.

В этот раз описание проб не очень богатое, т.к. он куда-то пропал из скайпа. По этому даю то что есть…

Координаты: 51.3978836N 30.0433964E

Результат замера: Pure cesium! 65.7 Бк Cs-137

Координаты: 51.3214669N 29.9468637E

Результат замера: 34.1 Бк Cs-137

Результат замера: 11.6 Бк Cs-137

Координаты: 51.2897816N 29.9207067E

Результат замера: 4.1 Бк Cs-137

Координаты: 50.6879347N 29.9705556E

Результат замера: 3.0 Бк Cs-137

Координаты: 51.4154298N 30.0502118E

Результат замера: Ничего не обнаружено.

PS. Elcat еще приготовил пробы для замера, но их я по техническим причинам получу несколько позже…

Издавна Xilinx-овские ПЛИСы славились тем что ISE прошивает их и отлаживают только через фирменные программаторы. На любых прочих, был большой костыль.

Самым распространенным в кругах любителей является “Xilinx Parallel Cable III”, как не сложно догодаться, это няшка для LPT порта. Видимо по этой самой причине, производитель выкладывает его схему прямо в ДШ.

Вроде не сложный совсем, но у меня этих портов нету, и шьет он далеко не все серии Xilinx’ов.

При этом никаких простых полноценных отладчиков с переферийным сканированием через USB я не знаю.

Так как я давно и очень основательно готовлюсь к освоению сего класса микросхем, как-то года 2-3 тому назад закупил китайскую подделку под “Xilinx Platform Cable USB”, т.к. оригинайный Platfom Cable стоит зачастую 300 баксов. Работоспособность китайского с новыми версиями среды разработки Xilinx ISE вызывала у меня опасения. Наконец дошли руки, расчихлил.

Естественно внутри неоригинальная плата и более простая плисина, нежели чем в оригинале

Как всегда…. чтобы прошить одну плисину, нужна другая плисина  Вообще странная тенденция… STM-ки прошивает STM-ка, Меги прошивает Мега. Xilinx’ы на общем фоне решили “выебнутся”, и помимо ПЛИСины впихнули на плату еще и монструозный МК от Cypress, хотя одной плисины помощьнее вполне хватило-бы.

Вообще странная тенденция… STM-ки прошивает STM-ка, Меги прошивает Мега. Xilinx’ы на общем фоне решили “выебнутся”, и помимо ПЛИСины впихнули на плату еще и монструозный МК от Cypress, хотя одной плисины помощьнее вполне хватило-бы.

Но в целом схемотехнический дизайн нормальный, без особых нюансов. Почти как в оригинале. Что не может не радовать.

Плата оригинала за 287,00 € выглядит так:

Подключенный таргет определяет, прошивает, и даже в принципе на адекватных скоростях JTAG интерфейса.

Так-что в принципе годная вещь, можно использовать. На Xilinx ISE 14.7 самой последней сборки, работает. К тому-же как я вижу он несколько подешевел за эти годы на али-экспрессе, сейчас китайцы просят за него около 25$.

Кстати, насколько мне известно, это единственный прошивальщик который китайцам удалось скопировать. Все последующие фирменные программаторы китайцам оказались неподвластны, насколько я знаю.

Elcat как-то обещал дать платку какого-то программатора, если пришлет на почту, добавлю в этот пост. Наверное речь шла о девайсе на базе FT2232H работающий как SVF Player.

.

PS. Для прошивки второго неотъемлемого компонента вычислительной платы BGM121, едет Segger J-Link EDU. Будет любопытно вскрыть его и посмотреть что внутри.

Дорисовал функционал таймеров в ПЛИСине. Решил пока не реализовывать загрузку констант по SPI, в принципе пока для первой редакции их можно прошивать сразу в ПЛИСину на этапе сборки.

Вообщем получилось нечто следующее:

Сигналы:

VHDL Кодом блока Impulse_control я вас пожалуй утруждать не буду, его всегда можно посмотреть тут. Весь нужный функционал вроде реализовал и занял он около 30% кристалла.

Симуляция работы показывает адекватные результаты:

Осталось развести плату. Благо это будет легко. Любой сигнал может быть посажен на любую ножку кроме питания, программирования и основной тактовой частоты.

Вывод: Плисины не так уж и страшны, как кажется на первый взгляд.

Посмотрел значит я на комменты к прошлой записи, и понял, что ничо никому нихрена не ясно…

Значит будем “прояснять”. Как пример, привожу код таймера который будет управлять накачкой. Занимает 22 макроячейчки в XC9500XL. В целом в коментах все описано, но основная суть сего таймера в:

Если напряжение меньше порога (лог.1 на входе Low_voltage), отсчитывать заданное время подачи импульса на транзистор(задается битовым значением на входах pulse_time[0..7]). По началу и завершению периода накачки выдать сигнал-уведомление work_timer, для дальнейшего анализа.

Этот небольшой код, генерирует вот такую партянку из логических элементов конфигурация которых в последствии прошиваются в ПЛИС:

При виде которой, у меня возникает только одна единственная ассоциация: Ебипетская сила!

По результатам симуляции можно видеть что код работает хорошо:

Осталось дело за малым, накодить второй модуль, который будет управлять цепочкой сброса заряда в аналоговой цепи, управлять стартом АЦП внутри МК, и считывать от МК по SPI конфигурацию параметров работы таймеров.

Начал потихоньку изучать программирование ПЛИСов, чтобы можно было обеспечить необходимую скорость управления аналоговой частью, но т.к. рисовать схемой нужный функционал, это несколько “топорно”, сижу изучаю VHDL.

К сожалению пока не нашел ни одной по настоящему хорошей книжки по этому языку, если у кого есть что-то на примете, просьба скинуть ссылки в комментариях.

В первом приближении, поражает синтез кусочка кода, в огромные наборы логики. Как пример 16-ти разрядный счетчик с проверкой условия:

Несколько недель я обмозговывал концепт нового детектора, в результате пришел к следующим теоретическим (пока теоретическим, т.к. плата не готова) выкладкам:

Подсистема питания блока развита до уровня “полный спектрометрический пиздец”, а именно стала содержать следующий минимально необходимый набор питаний:

PS.На АЦП и полноценную плисину денег уже нехватило….  Поэтому решил выжать предельно возможные скорости из EFR32, передав ему в подчинение свою собственную CPLD-шку, чтобы хоть как-то реализовать нужное управление временными характеристиками на этом говне.

Поэтому решил выжать предельно возможные скорости из EFR32, передав ему в подчинение свою собственную CPLD-шку, чтобы хоть как-то реализовать нужное управление временными характеристиками на этом говне.

Сразу давать пачкой такие схемы бесполезно, мозг взорвется  Поэтому начну с малого, с питания ФЭУ. Чтоб вы за недельку ее обдумали.

Поэтому начну с малого, с питания ФЭУ. Чтоб вы за недельку ее обдумали.

Неделя размышлений не прошла даром  Решил не брать лантан, а лучше закупить хороших деталек на новые проекты.

Решил не брать лантан, а лучше закупить хороших деталек на новые проекты.

Мне много кто из вас высказывал предположение, что разработки серии Микрон, это дорого. Нет, смею Вас заверить, это еще довольно дешево, по сравнению с моим новым “шоппинг” списком.

Теперь сотрудникам компаний Linear, Vishay, Panasonic, Harwin могут смело выплатить зарплату, c моих заказов

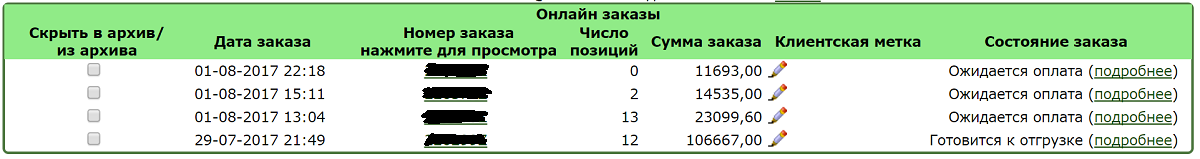

Некоторые из Вас уже познакомились с продукцией Linear по проекту Модуль-АС v.2.2, и понимают о чем я  А для остальных, маленький скриншот….

А для остальных, маленький скриншот….

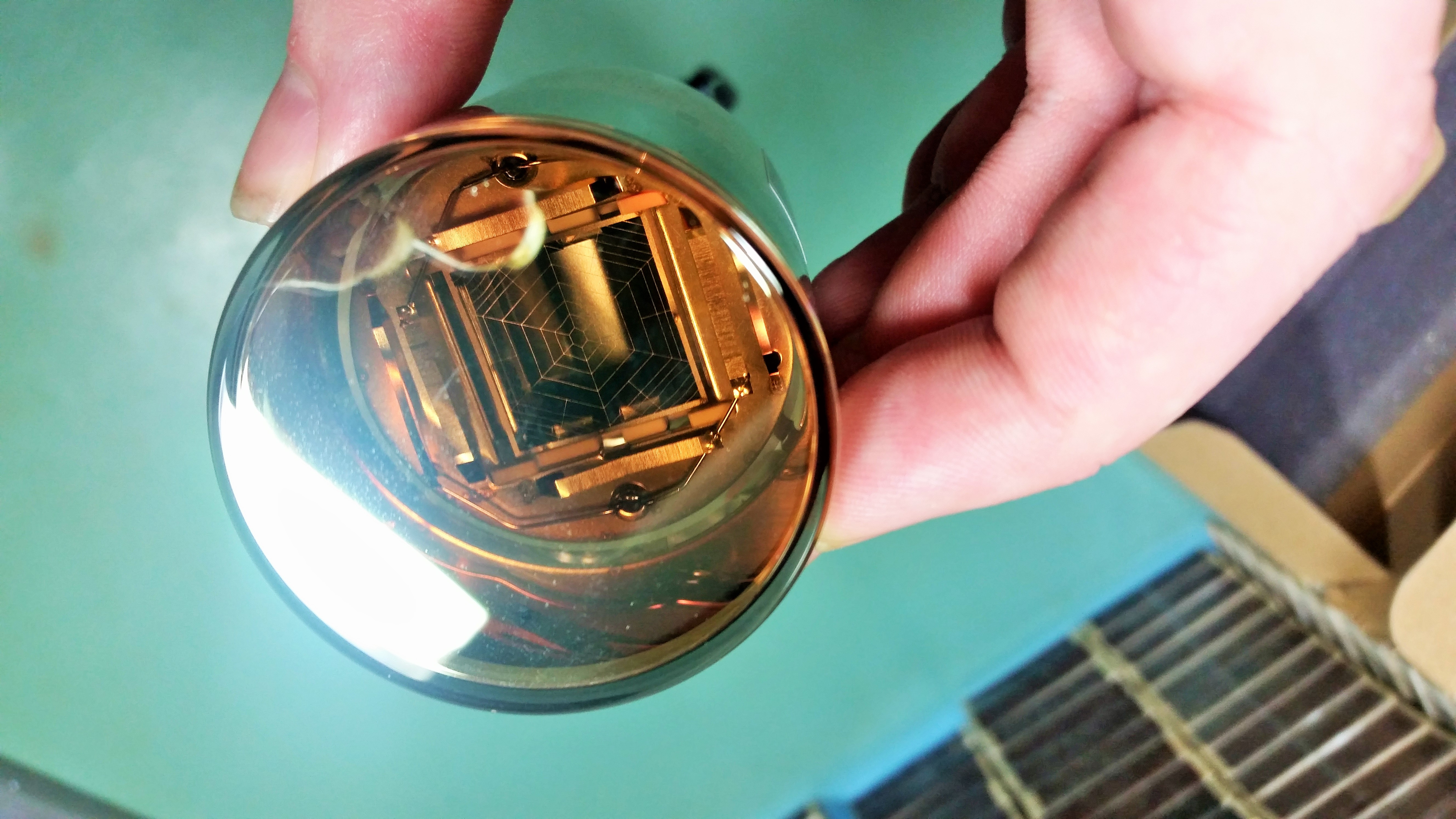

Приехала няшка Hamamatsu R6231-01

Скоро от Matrix’а должна приехать еще и панелька под маленькие хамаматцы, и я искренне надеюсь все-же получить маленькую R6095, т.к. доплатил барыгам из Бандеролька 10 баксов.

Получил образцы от Joosphp, надо будет найти времечко, заняться ими.

Приехал кристалл СДН.17.40.80, который оказался 6.5%, что весьма неплохо.

UPD: Чуть не забыл… ну как-же без миниатюрных няшек… без них никак!

Начинают приходить MMCX разъемы. А вы как хотели… наносекундные фронты с амплитудами в милливольты…. всетаки беземкостной дизайн пре-амплифаера на ФЭУ…. это вам не хухры-мухры… тут каждый проводок к 50-ти омному импедансу приводить надо… Ради согласования, похоже и плату придется четерехслойку заказывать. На двухслойке 50-ти омные трассы на нужные частоты развести почти нереально, слишком толстый препрег. Вообщем, тонна заморочек всяких. Да там еще и BGM121 дышит в затылок своими 2.4 ГГц, там уж полюбому 50-ти омные трассы и кабели до внешней антенны класть.